应用环境失效 - 静电放电(ESD)损伤

失效背景描述

某批次 MCU 芯片在客户端应用部署后,现场反馈出现特定 I/O 端口对地漏电现象,且失效模式具有一致性。

失效分析关键步骤

01. 外观检查:芯片封装完好,无划痕、裂纹等物理损伤。

02. 电性验证:确认失效品漏电I/O端口反向漏电流远超规格值。

03. 定位分析:利用OBIRCH锁定漏电点附近的异常发热“热点”。

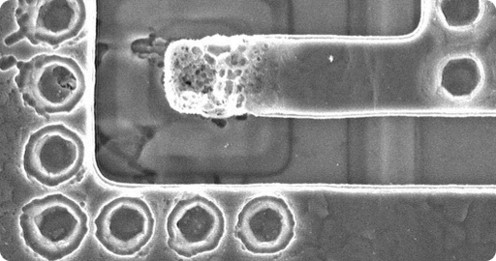

04. 显微观察:结合SEM发现热点区域金属互连层存在飞溅状熔断痕迹。

失效机理解析

静电放电产生的瞬间高压大电流,超过了芯片ESD保护电路的承受极限,导致栅氧化层击穿或引发闩锁效应,最终造成局部电路永久性烧毁。